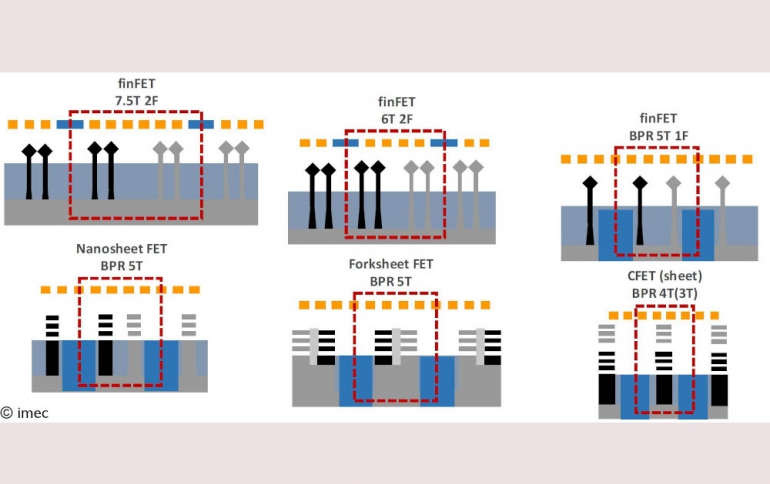

Imec Presents Forksheet device as a Solution to Push Scaling Towards the 2nm Technology Node

This week, at the 2019 IEEE International Electron Devices Meeting, imec presents first standard cell simulation results of its forksheet device designed for sub-3nm logic technology nodes.

Compared to nanosheet devices, the reduced n-to-p spacing results in a 10 percent performance increase. When combined with scaling boosters, the new device architecture will bring logic standard cell height down to 4.3 tracks, which combined with cell template optimization can result in more than 20 percent area reduction. The results value the forksheet architecture as a potential solution to extend the scalability of nanosheet structures beyond the 3nm logic technology node.

The forksheet device has recently been proposed by imec as a natural extension of vertically stacked lateral gate-all-around nanosheet devices. Contrary to the gate-all-around nanosheet device, in the forksheet, the nanosheets are now controlled by a tri-gate forked structure, realized by introducing a dielectric wall in between the P- and NMOS devices before gate patterning. This wall physically isolates the p-gate trench from the n-gate trench, allowing a much tighter n-to-p spacing – a challenge that could not be answered with FinFET or nanosheet structures. Because of this reduced n-to-p separation, the forksheet is expected to have superior area and performance scalability.

For the first time, standard cell simulations confirm this excellent power-performance-area (PPA) potential of the forksheet device architecture. The device under study targets imec’s 2nm technology node, using a contacted gate pitch of 42nm and a 5T standard cell library with a metal pitch of 16nm. The proposed design includes scaling boosters such as buried power rails and wrap around contacts. Compared to a nanosheet device, a 10 percent speed gain (at constant power) and a 24 percent power reduction (at constant speed) is reported. The performance boost can be partly explained by a reduced miller capacitance, resulting from a smaller gate-drain overlap. Finally, the n-to-p separation reduction can be used to reduce the track height from 5T to 4.3T. Further layout optimization exploiting the structure of the device enables more than 20 percent cell area reduction. When implemented in an SRAM design, the simulations reveal a combined cell area scaling and performance increase of 30 percent for 8nm p-n spacing.

“As industry scales from planar to FinFET to vertically stacked nanosheets, the fork-sheet concept is considered non-disruptive extension”, says Julien Ryckaert, Program director 3D hybrid scaling at imec. “The nanosheet device has mainly been introduced to improve electrostatic control and drive strength. But both for FinFET and nanosheet architectures feature a large n-to-p device separation distance hindering further scalability. The forksheet architecture is one way to address this challenge and can be considered the ultimate logic ‘universal’ CMOS device beyond 2nm. Continuing scaling beyond the forksheet device, we propose the complementary FET (or CFET) as a device cadidate.”

The process flow for the forksheet is similar to the one of a nanosheet device, with only limited additional process steps.

The results will be presented at IEDM2019 on Wednesday Dec 11, session 36.5 (3:15 p.m.).