| Message Text: |

Toshiba is launching three new TZ2100 application processors, the latest additions to its ApP Lite family?s ARM Cortex-A9-based TZ2000 series.

The TZ2100 high performance application processors support enhanced sound and image data-mining, along with communications and security functions.

TZ2100 can operate at a maximum frequency at 600MHz and can be used in a wide range of products such as the embedded devices, handheld devices, and industrial equipment.

Toshiba will start sampling the processors from mid-December, with mass production scheduled to start in June, 2015.

Key Features

- ARM Cortex-A9 operating at 600MHz

- L1 Cache: 32KByte, L2 Cache: 128KByte, Embedded FPU

- 300MHz version is also available.

- Accommodates DDR3-800/DDR3L-800 16bit width

- Toshiba's power-saving technology enables long time data back-up and RTC operation

- Enables long time data back-up and RTC operation with one single coin cell battery.

- Camera input, graphics and LCD output

- Suitable specification for applications such as panel control devices.

- Secure boot system and data encryption function

- Secure system uses encryption circuit is available as an option. Incorporating program area in a chip can be robust against data falsifying and hacking.

- 1MByte SRAM built-in

- 1MByte of built-in SRAM supports processing of start-up code and data during program execution, without any need for external DRAM.

- External expanded bus interface

- Supports use of memory with an external connection, which is necessary for amusement devices and industrial equipment

Specifications

Main Specifications |

| Part Number |

|

TZ2002XBG |

|

TZ2003XBG |

|

TZ2100XBG |

|

TZ2101XBG |

|

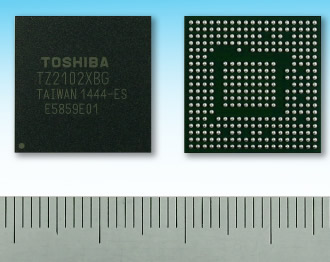

TZ2102XBG |

| CPU |

|

ARM Cortex-A9 MPCore

L1I Cache:

16KByte

L1D Cache: 16KByte |

|

ARMCortex-A9 MPCore

L1I Cache:

32KByte, L1D Cache: 32KByte

L2 Cache: 128KByte |

| Max Operating Frequency |

|

200MHz |

|

300MHz |

|

600MHz |

| FPU(Floating Point Unit) |

|

Not integrated |

|

Integrated |

| Secure Boot System Control, Encrypt Data Function |

|

Non-supported |

|

Supported |

|

Non-supported |

|

Supported |

|

Non-supported |

| RAM |

|

1MByte SRAM |

|

1MByte SRAM

32KByte SRAM(for Back-up) |

| DRAM Controller |

|

DDR3/DDR3Lx8bit |

|

DDR3/DDR3Lx16bit |

| External Extended Bus Interface |

|

Unintegrated |

|

Address: 27bit, Data:32bit |

| 2D Graphic Engine |

|

Toshiba original graphics accelerator |

| LCD Controller |

|

WVGA (800x480 pixel) 60fps, 24bit Parallel I/F |

| High Speed Interface Controller |

|

USB2.0 host interface, USB2.0 device interface, 10/100 Ethernet MAC |

| Peripheral Functions |

|

DMA controller, Timer/Counter, RTC |

| Peripherals |

|

UARTx4, I2C5, I2Sx2, SPIBx4, PWMx5,

12bitADCx4, SDIOx2, eMMCx1, GPIO |

|

Camera I/F, UARTx4, I2Cx4, I2Sx2, SPIMx7,

SPIBx2,PWMx6, 12bitADCx4, SDIOx3, eMMCx1, GPIO |

| Power Supply Voltage |

|

Core=1.1V, I/O=3.3V |

|

Core=1.1V, I/O=3.3V |

| Package |

|

LFBGA 280pin

15mmx15mm, 0.8mm pitch |

|

LFBGA 310pin

16mmx16mm, 0.8mm pitch |

| Production Status |

|

Mass production |

|

Mass production from June 2015 |

|