Elpida Integrates Error Correction Circuit in DRAM

Elpida Memory, Inc has developed SSR (Super Self Refresh) technology which achieves a reduction in DRAM's self refresh current to about 1/60 that of the company's conventional product.

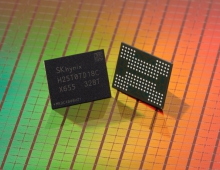

The company has also developed a 256-Mbit DDR synchronous DRAM (SDRAM) product, the EDD2516KCTA, using this technology. Elpida said this chip achieves the lowest self refresh current in the DDR SDRAM industry.

In an effort to reduce self refresh current, Elpida broadly extended the conventional model's internal refresh interval. When extending the refresh interval in the conventional DRAM, charge in capacitors becomes lost during the longer interval, and therefore causes imprecise readings. However, Elpida discovered that data only becomes garbled within some memory cells, which have a poor ability to preserve charge. The company accordingly integrated an error correction circuit in a DRAM device so that it could correct the data that becomes garbled under a longer refresh interval.

The EDD2516KCTA's data rate complies with DDR400. In other words, the maximum data rate per pin is 400Mbps. The company expects it to be used in applications such as car navigation systems, PDAs and Flash EEPROM discs. Its self refresh current (IDD6) is as low as 40m΅A at 25 degrees, 150m΅A at 70 degrees and 250muA at 85 degrees, compared to a large 3mA required by the conventional product (DDR SDRAM) at 0-70 degrees.

Production of the EDD2516KCTA uses 110nm CMOS process technology. The company has already started sample shipments, with volume production slated to start in March 2005. A 512Mb product, an MCP of this 256Mb chip, is also available.

From NE Asia Online